Features

- 4×100 Gigabit Ethernet (4×106.25 Gbit/s)

- Compliant to 26.5625 GBd PAM4,

- 400GAUI-8 (Aggregation mode) and

- 4x100GAUI-2 (Breakout mode) Electrical Interface specifications

- MPO-12 with 8° angled end face

- Low power consumption: 12 W max

- Operating case temperature: 0 to 70 °C

- Two-wire common management interface

Description

Wavesplitter’s WST-QD4-DR4+C is a 4x100G QSFP56-DD optical transceiver that enables high 4 parallel 100 GbE port densities owing to its compact size and low power consumption. WST-QD4-DR4+C may be used in network applications, such as Ethernet switches and IP routers, at transmission distances of up to 2 km over parallel single mode fiber (SMF).

The form factor of WST-QD4-DR4+C - QSFP56-DD Type 2 - is compliant with the hardware and management interface specifications (MIS) of the QSFP-DD multi-source agreement (MSA). QSFP-DD modules can support up to eight electrical lanes on the host interface, which is double the number of lanes supported by QSFP28 or QSFP+ modules. The unique feature of QSFP-DD ports is that they are mechanically and electrically compatible with QSFP28 and QSFP+. Hence, the same port can be used to support multiple generations of modules and data rates if the networking hardware is designed for such operation.

WST-QD4-DR4+C transmits data in compliance with the optical interface specification 100GBASE-FR1 defined by IEEE P802.3cu-D2p2 per each lane. 100GBASE-FR1 specifies the use of 4-level pulse amplitude modulation (PAM4) at 53.125 Gbaud operating at each of 4 channels with 1.3 µm wavelength range. The bit rate per lane is 106.25 Gbit/s, which produces a total data rate of 425 Gbit/s in 4 lanes.

The electrical interface is in compliance with 400GAUI-8 specified in IEEE 802.3-2018 Section 8 and 4x100GAUI-2 specified in IEEE 802.3-2018 Section 6/IEEE P802.3cd-2018. 400GAUI-8 specifies the use of eight differential electrical lanes operating at 26.5625 Gbaud PAM4 per lane. The bit rate per lane is 53.125 Gbit/s, resulting in an aggregate data rate of 425 Gbit/s that matches the optical line interface. An internal gear box IC converts between the eight lanes of the host interface and the four lanes of the line interface. 100GAUI-2 specifies the use of two differential electrical lanes operating at 26.5625 Gbaud PAM4 per lane. The bit rate per lane is 53.125 Gbit/s, resulting in a data rate of 106.25 Gbit/s that matches the optical interface per lane. An internal gear box IC converts between the two lanes of the host interface and the one lane of the line interface.

The bit error ratio (BER) of the optical interface is required by 100GBASE-FR1 to be less than 2.4 x 10-4. Hardware using WST-QD4-DR4+C must have RS(544,514) forward error correction (FEC) capability to meet the frame loss ratio requirements. The specification for RS(544,514) FEC may be found in IEEE 802.3-2018 Section 8.

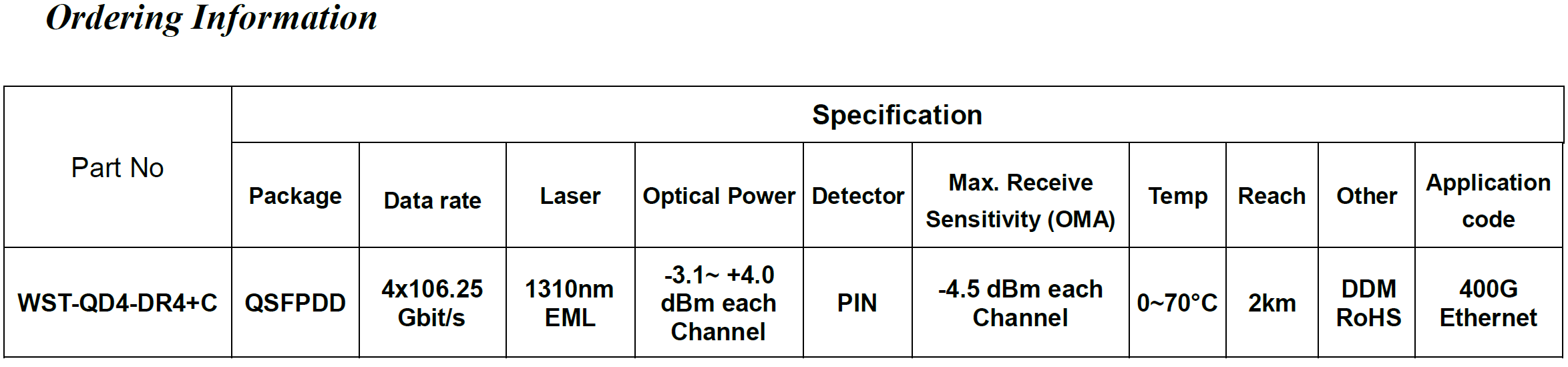

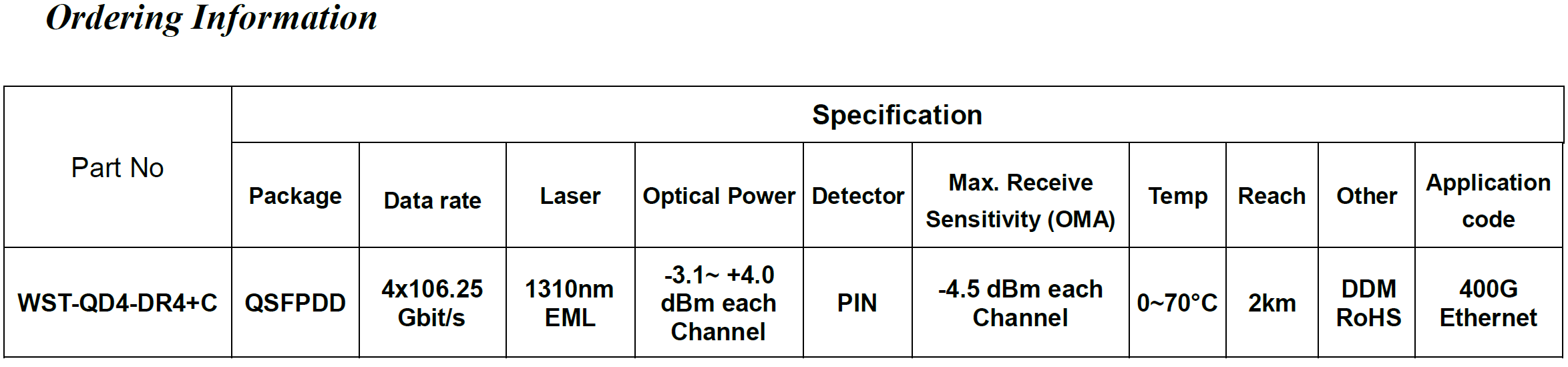

Specification