# **Data Sheet**

# 400G QSFP-DD FR4 2km Transceiver Module P/N: WST-QD4-FR4-C

# **Applications:**

- Data Center 400GE 2km SMF links

- Switch/Router interconnections

#### Standards:

- Compliant to QSFP-DD MSA hardware specification

- IEEE 802.3bs-2017

- CMIS 4.0 management interface

- 100G Lambda MSA "400G-FR4 Technical Specification Rev 2.0"

#### Features:

- 400 Gigabit Ethernet (425 Gbit/s)

- Compliant to 53.125 GBd PAM4 x 4 wavelength 400G-FR4 optical interface specification

- Compliant to 26.5625 GBd PAM4 x 8 lane 400GAUI-8 Electrical Interface specification

- Transmission distance of up to 2 km over duplex SMF.

- Low power consumption: 12 W max

- Operating case temperature: 0 to 70°C

- Hot Z-Pluggable to 76-pad QSFP-DD electrical connector

- Latching mechanism: Pull tab

- Two-wire common management interface

- RoHS compliant

### Description

Wavesplitter's WST-QD4-FR4-C is a 400G QSFP56-DD optical transceiver that enables high 400 GbE port densities owing to its compact size and low power consumption. WST-QD4-FR4-C may be used in network applications, such as Ethernet switches and IP routers, at transmission distances of up to 2 km over duplex single mode fiber (SMF).

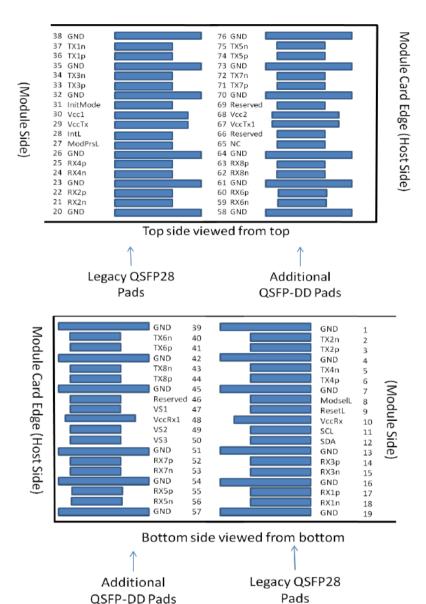

The form factor of WST-QD4-FR4-C - QSFP56-DD Type 2 - is compliant with the hardware and management

interface specifications (MIS) of the QSFP-DD multi-source agreement (MSA). QSFP-DD modules can support up to eight electrical lanes on the host interface, which is double the number of lanes supported by QSFP28 or QSFP+ modules. The unique feature of QSFP-DD ports is that they are mechanically and electrically compatible with QSFP28 and QSFP+. Hence, the same port can be used to support multiple generations of modules and data rates if the networking hardware is designed for such operation.

WST-QD4-FR4-C transmits data in compliance with the optical interface specification 400G-FR4 defined by the 100G Lambda MSA. 400G-FR4 specifies the use of 4-level pulse amplitude modulation (PAM4) at 53.125 Gbaud operating at four wavelengths on a course wavelength division multiplexed (CWDM) grid. The bit rate per lane is 106.25 Gbit/s, which produces an aggregate data rate of 425 Gbit/s.

The electrical interface is in compliance with 400GAUI-8 specified in IEEE 802.3bs-2017. 400GAUI-8 specifies the use of eight differential electrical lanes operating at 26.5625 Gbaud PAM4 per lane. The bit rate per lane is 53.125 Gbit/s, resulting in an aggregate data rate of 425 Gbit/s that matches the optical line interface. An internal gear box IC converts between the eight lanes of the host interface and the four lanes of the line interface.

The bit error ratio (BER) of the optical interface is required by 400G-FR4 to be less than  $2.4 \times 10^{-4}$ . Hardware using WST-QD4-FR4-C must have KP4 forward error correction (FEC) capability to meet the frame loss ratio requirements of 400 GbE. The specification for KP4-FEC may be found in IEEE 802.3bs-2017.

#### Absolute Maximum Ratings

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings will cause permanent damage and/or adversely affect device reliability.

| Parameter                          | Symbol | Min | Max | Units | Notes |

|------------------------------------|--------|-----|-----|-------|-------|

| Storage Temperature                | TS     | -40 | 85  | °C    |       |

| Power Supply Voltage               | VCC    | 0   | 3.6 | V     |       |

| Optical Receiver Input (each lane) |        |     | +5  | dBm   |       |

#### **Recommended Operating Conditions**

| Parameter                      | Symbol              | Min   | Typical | Max   | Units | Notes         |

|--------------------------------|---------------------|-------|---------|-------|-------|---------------|

| Operating Case Temperature     | TOP                 | 0     |         | 70    | °C    |               |

| Supply Voltage Noise Tolerance | PSNR <sub>mod</sub> |       |         | 66    | mV    | 10 Hz –10 MHz |

| Power Supply Voltage           | VCC                 | 3.135 | 3.3     | 3.465 | V     |               |

| Power Consumption              | P_6                 |       |         | 12    | W     |               |

WST-QD4-FR4-C

| Instantaneous peak current | Icc_ip_6 |  | 4800   | mA |              |

|----------------------------|----------|--|--------|----|--------------|

| Sustained peak current     | Icc-sp_6 |  | 3960   | mA |              |

| Supply Current             | Icc-6    |  | 3827.8 | mA | Steady state |

#### **Electrical Characteristics**

The following electrical characteristics are defined over the Recommended Operating Environment unless otherwise specified.

| Parameter                                        | Min         | Typical     | Max  | Units | Notes   |

|--------------------------------------------------|-------------|-------------|------|-------|---------|

| Module output (each lane, at TP4) (Note 1)       |             |             |      |       |         |

| Signaling Rate, each Lane                        | 26.5625     | 5 ± 100 ppm |      | GBd   |         |

| Differential pk-pk input voltage tolerance (min) | 900         |             |      | mV    | at TP1a |

| Differential termination mismatch                |             |             | 10   | %     | at TP1  |

| Single-ended input voltage tolerance range       | -0.4 to 3.3 |             |      | V     | at TP1a |

| DC common mode voltage                           | -350        |             | 2850 | mV    | at TP1  |

| Receiver (each lane, at TP4)                     |             |             |      |       |         |

| Signaling Rate, each Lane                        | 26.562      | 5 ± 100 ppm | 1    | GBd   |         |

| Differential output voltage                      |             |             | 900  | mV    |         |

| Near-end ESMW (Eye symmetry mask width)          | 0.265       |             |      | UI    |         |

| Near-end Eye height, differential                | 70          |             |      | mV    |         |

| Far-end ESMW (Eye symmetry mask width)           | 0.2         |             |      | UI    |         |

| Far-end Eye height, differential                 | 30          |             |      | mV    |         |

| Differential termination mismatch                |             |             | 10   | %     |         |

| Transition time (20% to 80%)                     | 9.5         |             |      | ps    |         |

| DC common mode voltage                           | -350        |             | 2850 | mV    |         |

| Differential output voltage                      |             |             | 900  | mV    |         |

#### Notes:

- 1. Electrical module output is squelched for loss of optical input signal.

- 2. IEEE Std 802.3-2018 Section 6.

# **Optical Characteristics**

| Parameter                          | Symbol          | Min    | Typical    | Max      | Units  | Notes        |

|------------------------------------|-----------------|--------|------------|----------|--------|--------------|

| Transmitter                        |                 |        |            |          |        |              |

|                                    |                 | 1264.5 |            | 1277.5   | nm     |              |

| N/                                 | ,               | 1284.5 |            | 1297.5   | nm     |              |

| Wavelength Assignment              | λς              | 1304.5 |            | 1317.5   | nm     |              |

|                                    |                 | 1324.5 |            | 1337.5   | nm     |              |

| Channel data rate                  | f <sub>DC</sub> |        | 106.25     |          | Gbit/s |              |

| Data Rate, each Lane               | f <sub>SG</sub> | 53     | .125 ± 100 | ppm      | GBd    | PSM4         |

| Side-mode suppression ratio        | SMSR            | 30     |            |          | dB     |              |

| Total average launch power         |                 |        |            | 9.3      | dBm    |              |

| Average launch power, each lane    |                 | -3.3   |            | 3.5      | dBm    | 1            |

| Outer Optical Modulation Amplitude |                 | 0.0    |            | 2.7      | dD.m   | 2            |

| (OMAouter), each lane              |                 | -0.3   |            | 3.7      | dBm    | 2            |

| Launch power in OMAouter minus     |                 | -1.7   |            |          | dBm    | For ER≧4.5dB |

| TDECQ, each lane                   |                 | -1.6   |            |          | UDIII  | For ER<4.5dB |

| Transmitter and dispersion eye     | TDECQ           |        |            | 3.4      | dB     |              |

| closure for PAM4, each lane        | IDECQ           |        |            | 5.4      | ub     |              |

| Average optical output power       | Poff            |        |            | -20      | dBm    |              |

| of OFF Transmitter, each lane      | 1 011           |        |            | -20      |        |              |

| Extinction Ratio, each lane        | ER              | 3.5    |            |          | dB     |              |

| RIN <sub>15.6</sub> OMA            |                 |        |            | -136     | dB/Hz  |              |

| Optical return loss tolerance      |                 |        |            | 17.1     | dB     |              |

| Transmitter reflectance            |                 |        |            | -26      | dB     |              |

| Receiver                           |                 |        |            |          |        |              |

| Average receive power, each lane   |                 | -7.3   |            | 3.5      | dBm    |              |

| Receive power (OMAouter) ,         |                 |        |            | 0.7      | ما ال  |              |

| each lane                          |                 |        |            | 3.7      | dBm    | 3            |

| Receiver reflectance               |                 |        |            | -26      | dB     |              |

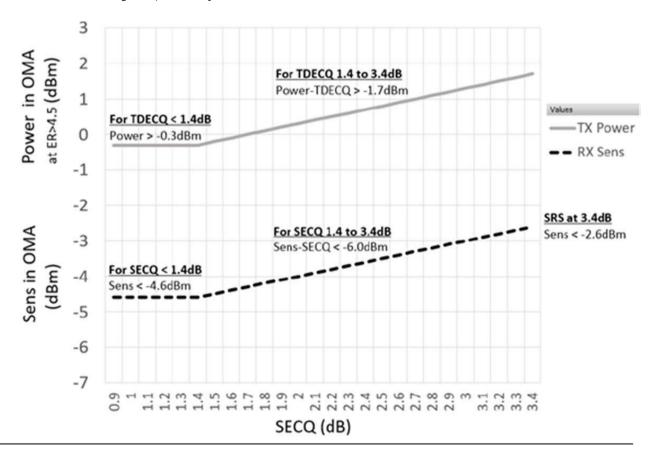

| Stressed receiver sensitivity,     |                 |        |            | Eigura E | dDm    | 2            |

| each lane (OMAouter)               |                 |        |            | Figure 5 | dBm    | 3            |

| Conditions of stressed receiver sensitivity test (note 8) |      |     |            |       |     |   |  |

|-----------------------------------------------------------|------|-----|------------|-------|-----|---|--|

| Stressed eye closure for                                  | 0500 |     | 0.04-0.4   |       | dB  | 4 |  |

| PAM4, lane under test                                     | SECQ |     | 0.9 to 3.4 |       |     | 4 |  |

| OMAouter of each aggressor lane                           |      | 1.5 |            |       | dBm | 4 |  |

| Assert                                                    |      | -30 |            | -10.3 | dBm |   |  |

| Deassert                                                  |      |     |            | -7.3  | dBm |   |  |

#### Notes:

- Average launch power, each lane (min) is informative and not the principal indicator of signal strength.

A transmitter with launch power below this value cannot be compliant; however, a value above this does not ensure compliance.

- 2. Even if the TDECQ < 1.4 dB for an extinction ratio of  $\geq$  4.5 dB or TDECQ < 1.3 dB for an extinction ratio of < 4.5 dB, the OMAouter (min) must exceed this value.

- 3. Forward Error Correction (FEC) is done at PCS layer outside QSFP56-DD modules and on the host IC, and the BER at optical input specified as Receiver sensitivity is therefore be 2.4E-4 without error correction as defined in 100G Lambda MSA Specification.

- 4. A compliant receiver shall have stressed receiver sensitivity (OMA outer), each lane values below the mask of Figure 5, for SECQ values between 0.9 and 3.4 dB.

# Pin Assignment

| Pin | Logic   | Symbol  | Description                         | Plug Sequence | Notes |

|-----|---------|---------|-------------------------------------|---------------|-------|

| 1   |         | GND     | Ground                              | 1B            | 1     |

| 2   | CML-I   | Tx2n    | Transmitter Inverted Data Input     | 3B            |       |

| 3   | CML-I   | Tx2p    | Transmitter Non-Inverted Data Input | 3B            |       |

| 4   |         | GND     | Ground                              | 1B            | 1     |

| 5   | CML-I   | Tx4n    | Transmitter Inverted Data Input     | 3B            |       |

| 6   | CML-I   | Tx4p    | Transmitter Non-Inverted Data Input | 3B            |       |

| 7   |         | GND     | Ground                              | 1B            | 1     |

| 8   | LVTTL-I | ModSelL | Module Select                       | 3B            |       |

# 400G QSFP-DD FR4 2km Transceiver Module WST-QD4-FR4-C

| 9  | LVTTL-I      | ResetL   | Module Reset                                                                        | ЗВ |   |

|----|--------------|----------|-------------------------------------------------------------------------------------|----|---|

| 10 | _ v ı ı ∟⁻1  | VccRx    | +3.3V Power Supply Receiver                                                         | 2B | 2 |

| 11 | LVCMOS-I/O   | SCL      | 2-wire serial interface clock                                                       | 3B |   |

| 12 | LVCMOS-I/O   | SDA      | 2-wire serial interface data                                                        | 3B |   |

|    | LVCIVIOS-I/O |          |                                                                                     |    | 4 |

| 13 |              | GND      | Ground                                                                              | 1B | 1 |

| 14 | CML-O        | Rx3p     | Receiver Non-Inverted Data Output                                                   | 3B |   |

| 15 | CML-O        | Rx3n     | Receiver Inverted Data Output                                                       | 3B | 1 |

| 16 |              | GND      | Ground                                                                              | 1B |   |

| 17 | CML-O        | Rx1p     | Receiver Non-Inverted Data Output                                                   | 3B |   |

| 18 | CML-O        | Rx1n     | Receiver Inverted Data Output                                                       | 3B |   |

| 19 |              | GND      | Ground                                                                              | 1B | 1 |

| 20 |              | GND      | Ground                                                                              | 1B | 1 |

| 21 | CML-O        | Rx2n     | Receiver Inverted Data Output                                                       | 3B |   |

| 22 | CML-O        | Rx2p     | Receiver Non-Inverted Data Output                                                   | 3B |   |

| 23 |              | GND      | Ground                                                                              | 1B | 1 |

| 24 | CML-O        | Rx4n     | Receiver Inverted Data Output                                                       | 3B |   |

| 25 | CML-O        | Rx4p     | Receiver Non-Inverted Data Output                                                   | 3B |   |

| 26 |              | GND      | Ground                                                                              | 1B | 1 |

| 27 | LVTTL-O      | ModPrsL  | Module Present                                                                      | 3B |   |

| 28 | LVTTL-O      | IntL     | Interrupt                                                                           | 3B |   |

| 29 |              | VccTx    | +3.3V Power supply transmitter                                                      | 2B | 2 |

| 30 |              | Vcc1     | +3.3V Power supply                                                                  | 2B | 2 |

| 31 | LVTTL-I      | InitMode | Initialization mode; In legacy QSFP applications, the InitMode pad is called LPMODE | 3B |   |

| 32 |              | GND      | Ground                                                                              | 1B | 1 |

| 33 | CML-I        | Тх3р     | Transmitter Non-Inverted Data Input                                                 | 3B |   |

| 34 | CML-I        | Tx3n     | Transmitter Inverted Data Input                                                     | 3B |   |

| 35 |              | GND      | Ground                                                                              | 1B | 1 |

| 36 | CML-I        | Tx1p     | Transmitter Non-Inverted Data Input                                                 | 3B |   |

| 37 | CML-I        | Tx1n     | Transmitter Inverted Data Input                                                     | 3B |   |

| 38 |              | GND      | Ground                                                                              | 1B | 1 |

| 39 |              | GND      | Ground                                                                              | 1A | 1 |

| 40 | CML-I        | Tx6n     | Transmitter Inverted Data Input                                                     | 3A |   |

| 41 | CML-I        | Тх6р     | Transmitter Non-Inverted Data Input                                                 | 3A |   |

| 42 |              | GND      | Ground                                                                              | 1A | 1 |

| 43 | CML-I        | Tx8n     | Transmitter Inverted Data Input                                                     | 3A |   |

# 400G QSFP-DD FR4 2km Transceiver Module WST-QD4-FR4-C

| 44 | CML-I | Tx8p     | Transmitter Non-Inverted Data Input | 3A |   |

|----|-------|----------|-------------------------------------|----|---|

| 45 |       | GND      | Ground                              | 1A | 1 |

| 46 |       | Reserved | For future use                      | 3A | 3 |

| 47 |       | VS1      | Module Vendor Specific 1            | 3A | 3 |

| 48 |       | VccRx1   | 3.3V Power Supply                   | 2A | 2 |

| 49 |       | VS2      | Module Vendor Specific 2            | 3A | 3 |

| 50 |       | VS3      | Module Vendor Specific 3            | 3A | 3 |

| 51 |       | GND      | Ground                              | 1A | 1 |

| 52 | CML-O | Rx7p     | Receiver Non-Inverted Data Output   | 3A |   |

| 53 | CML-O | Rx7n     | Receiver Inverted Data Output       | 3A |   |

| 54 |       | GND      | Ground                              | 1A | 1 |

| 55 | CML-O | Rx5p     | Receiver Non-Inverted Data Output   | 3A |   |

| 56 | CML-O | Rx5n     | Receiver Inverted Data Output       | 3A |   |

| 57 |       | GND      | Ground                              | 1A | 1 |

| 58 |       | GND      | Ground                              | 1A | 1 |

| 59 | CML-O | Rx6n     | Receiver Inverted Data Output       | 3A |   |

| 60 | CML-O | Rx6p     | Receiver Non-Inverted Data Output   | 3A |   |

| 61 |       | GND      | Ground                              | 1A | 1 |

| 62 | CML-O | Rx8n     | Receiver Inverted Data Output       | 3A |   |

| 63 | CML-O | Rx8p     | Receiver Non-Inverted Data Output   | 3A |   |

| 64 |       | GND      | Ground                              | 1A | 1 |

| 65 |       | NC       | No Connect                          | 3A | 3 |

| 66 |       | Reserved | For future use                      | 3A | 3 |

| 67 |       | VccTx1   | 3.3V Power Supply                   | 2A | 2 |

| 68 |       | Vcc2     | 3.3V Power Supply                   | 2A | 2 |

| 69 |       | Reserved | For Future Use                      | 3A | 3 |

| 70 |       | GND      | Ground                              | 1A | 1 |

| 71 | CML-I | Tx7p     | Transmitter Non-Inverted Data Input | 3A |   |

| 72 | CML-I | Tx7n     | Transmitter Inverted Data Input     | 3A |   |

| 73 |       | GND      | Ground                              | 1A | 1 |

| 74 | CML-I | Тх5р     | Transmitter Non-Inverted Data Input | 3A |   |

| 75 | CML-I | Tx5n     | Transmitter Inverted Data Input     | 3A |   |

| 76 |       | GND      | Ground                              | 1A | 1 |

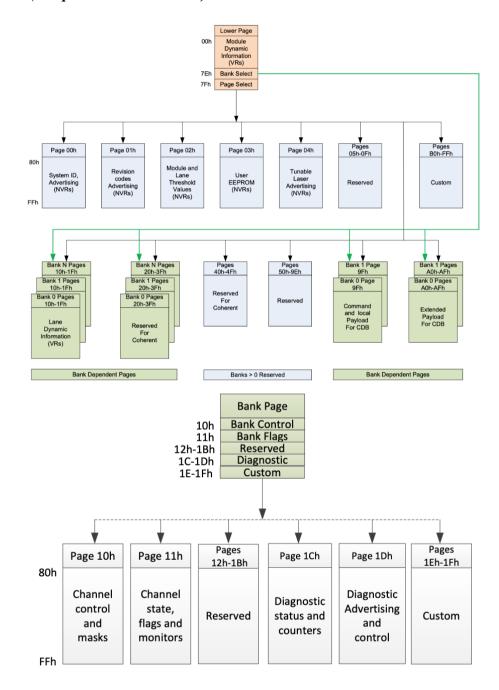

# MEMORY MAP (compliant CMIS Rev. 4.0)

# Digital Diagnostic Functions

The following digital diagnostic characteristics are defined over the normal operating conditions unless otherwise specified.

| Parameter                               | Symbol       | Min  | Max | Units | Notes                            |

|-----------------------------------------|--------------|------|-----|-------|----------------------------------|

| Temperature monitor absolute error      | DMI_Temp     | -3   | 3   | °C    | Over operating temperature range |

| Supply voltage monitor absolute error   | DMI _VCC     | -0.1 | 0.1 | V     | Over full operating range        |

| Channel RX power monitor absolute error | DMI_RX_Ch    | -2   | 2   | dB    | 1                                |

| Channel Bias current monitor            | DMI_Ibias_Ch | -10% | 10% | mA    |                                  |

| Channel TX power monitor absolute error | DMI_TX_Ch    | -2   | 2   | dB    | 1                                |

#### Notes:

1. Due to measurement accuracy of different single mode fibers, there could be an additional +/-1 dB fluctuation, or a +/-3 dB total accuracy.

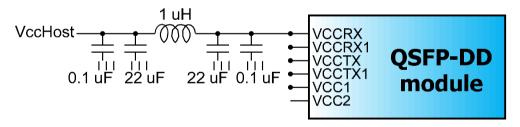

# Recommended Power Supply Filter

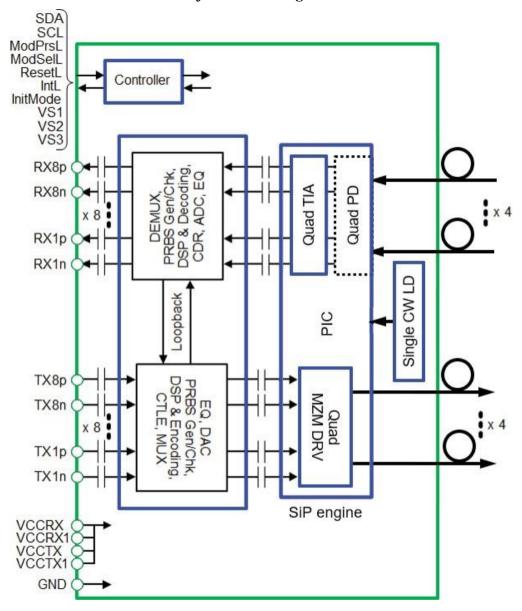

# Recommended Host - Transceiver Interface Block Diagram

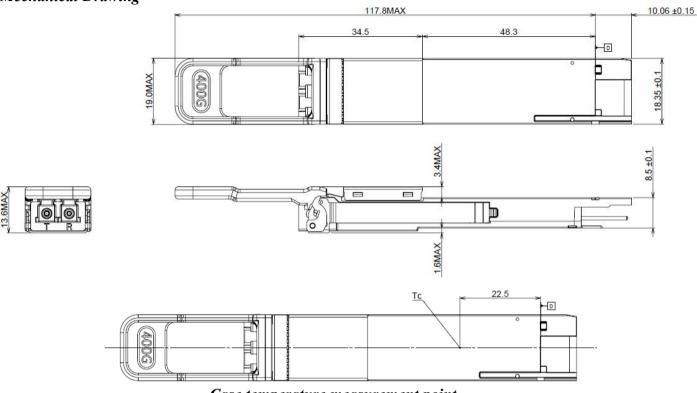

# **Mechanical Drawing**

Optical Interface is dual LC connector. Looking into the connector, transmitter is on the left.

Unit: mm

# **Ordering Information**

|               |         | Specification                       |                                             |                                   |          |                                |        |       |             |                  |  |  |

|---------------|---------|-------------------------------------|---------------------------------------------|-----------------------------------|----------|--------------------------------|--------|-------|-------------|------------------|--|--|

| Part No       | Package | Data rate                           | Laser                                       | Optical Power                     | Detector | Max. Receive<br>Sensitivity    | Temp   | Reach | Other       | Application code |  |  |

| WST-QD4-FR4-C |         | 106.25Gbps<br>(PAM4) per<br>channel | 1271nm<br>1291nm<br>1311nm<br>1331nm<br>EML | -3.2~ +4.4<br>dBm each<br>Channel | PIN      | -7.2~ +4.4 dBm<br>each Channel | 0~70°C | 2km   | DDM<br>RoHS | 400G<br>Ethernet |  |  |

# **Modification History**

| Revision | Date        | Description                 | Originator | Review    | Approved   |

|----------|-------------|-----------------------------|------------|-----------|------------|

| V1.0     | 08-Jul-2021 | New Issue                   | ShaoYu Lee | Tom Tang  | Wayne Liao |

| V1.1     | 14-Oct-2022 | Update Pin Assignment       | ShaoYu Lee | Tom Tang  | Wayne Liao |

| V1.2     | 19-Feb-2024 | Updated format, memory map. | Joanne Ni  | Ken Cheng | Tom Tang   |

**Taipei Headquarters** 16F-5, No. 75, Sec. 1, Xintai 5th Rd., Xizhi Dist., New Taipei City 22101, Taiwan

Tel: +886-2-2698-7208

Fax: +886-2-2698-7210 Email: sales@wavesplitter.com Website: https://wavesplitter.com/